# 250mA Single LDO with Low $I_Q$ , Low Noise and High PSRR LDO

#### **ISL9021A**

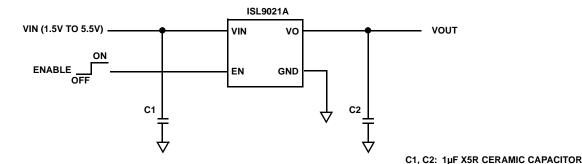

The ISL9021A is a single LDO, which provides high performance, low input voltage and high PSRR. It delivers guaranteed continuous 250mA load current and is stable with 1 $\mu$ F to 4.7 $\mu$ F of output capacitance (±30%) with an ESR range of 5m $\Omega$  to 400m $\Omega$ .

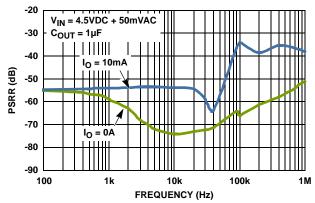

The input voltage range for the ISL9021A is between 1.5V to 5.5V and the output voltage comes in many fixed voltage options with  $\pm 1.8\%$  accuracy over-temperature, line and load ranges. The ISL9021A has typical PSRR of 75dB @ 10kHz and 50dB @ 1MHz.

The reverse current protection feature prevents current from flowing back to the power source when the output voltage is pulled higher than the input.

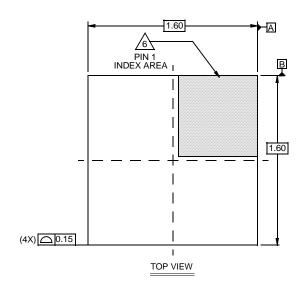

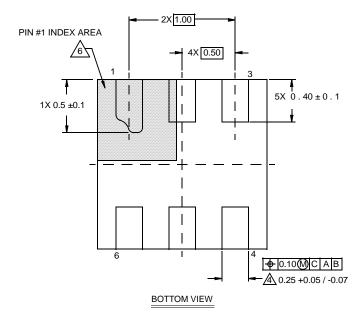

The ISL9021A is offered in tiny 4-bump 2mmx2mm WLCSP and 1.6mmx1.6mm 6 Ld  $\mu$ TDFN packages.

### **Related Literature**

See FN6867, ISL9021 "250mA Single LDO with Low IQ, Low Noise and High PSRR LDO"

1

### **Features**

- High Performance LDO with 250mA Guaranteed Continuous Output Current

- Input Voltage Range: 1.5V to 5.5V

- · Output Voltage Range: 1.2V to 3.3V

- High PSRR: 75dB @ 10kHz, 50dB @ 1MHz

- Low Quiescent Current: 35µA

- Dropout Voltage: <150mV @ 250mA

- Stable with 1µF to 4.7µF Output Capacitance (±30%) with an ESR range of 5m $\Omega$  to 400m $\Omega$

- ±1.8% Output Accuracy Over-Temperature/Load/Line

- Soft-start Limits Input Current Surge During Enable

- · Current Limit and Overheat Protection

- -40°C to +85°C Operating Temperature Range

- Available in 2mmx2mm 4-bump WLCSP Package and 1.6mmx1.6mm 6 Ld µTDFN

- · Pb-free (RoHS compliant)

### **Applications**

- PDAs, Cell Phones and Smart Phones

- Portable Instruments, MP3 Players

- · Handheld Devices including Medical Handhelds

FIGURE 1. TYPICAL APPLICATION

### **Block Diagram**

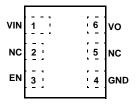

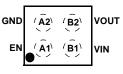

### **Pin Configurations**

ISL9021A (6 LD 1.6x1.6 µTDFN) TOP VIEW

ISL9021A (4 BALL 2X2 WLCSP) TOP VIEW

### **Pin Descriptions**

| PIN<br>NAME | µTDFN<br>PIN# | WLCSP<br>PIN# | DESCRIPTION                                                     |

|-------------|---------------|---------------|-----------------------------------------------------------------|

| VIN         | 1             | B1            | IC Supply/LDO Input. Connect a 1μF capacitor to GND.            |

| NC          | 2, 5          | -             | No Connect.                                                     |

| GND         | 4             | A2            | System ground pin.                                              |

| EN          | 3             | A1            | LDO Enable. When this signal goes high, the LDO is turned on.   |

| VO,<br>VOUT | 6             | B2            | LDO Output. Connect a 1µF to 4.7µF capacitor to GND.            |

| PAD         | -             | -             | For µTDFN package option only. Connect it to the system ground. |

### **Ordering Information**

| PART NUMBER<br>(Notes 1, 4) | PART<br>MARKING | V <sub>O</sub> Voltage<br>(V) | TEMP RANGE (°C) | PACKAGE<br>(Pb-free) | PKG.<br>DWG. # |

|-----------------------------|-----------------|-------------------------------|-----------------|----------------------|----------------|

| ISL9021AIINZ-T (Note 2)     | 021N            | 3.3                           | -40°C to +85°C  | 4 Ball 2x2 WLCSP     | W2X2.4         |

| ISL9021AIIMZ-T (Note 2)     | 021M            | 3.0                           | -40°C to +85°C  | 4 Ball 2x2 WLCSP     | W2X2.4         |

| ISL9021AIIKZ-T (Note 2)     | 021K            | 2.85                          | -40°C to +85°C  | 4 Ball 2x2 WLCSP     | W2X2.4         |

| ISL9021AIIFZ-T (Note 2)     | 021F            | 2.5                           | -40°C to +85°C  | 4 Ball 2x2 WLCSP     | W2X2.4         |

| ISL9021AIICZ-T (Note 2)     | 021C            | 1.8                           | -40°C to +85°C  | 4 Ball 2x2 WLCSP     | W2X2.4         |

| ISL9021AIIBZ-T (Note 2)     | 021B            | 1.5                           | -40°C to +85°C  | 4 Ball 2x2 WLCSP     | W2X2.4         |

| ISL9021AIIWZ-T (Note 2)     | 021W            | 1.2                           | -40°C to +85°C  | 4 Ball 2x2 WLCSP     | W2X2.4         |

| ISL9021AIRUNZ-T (Note 3)    | V6              | 3.3                           | -40°C to +85°C  | 6 Ld μTDFN           | L6.1.6X1.6     |

| ISL9021AIRUMZ-T (Note 3)    | V5              | 3.0                           | -40°C to +85°C  | 6 Ld μTDFN           | L6.1.6X1.6     |

| ISL9021AIRUKZ-T (Note 3)    | V4              | 2.85                          | -40°C to +85°C  | 6 Ld μTDFN           | L6.1.6X1.6     |

| ISL9021AIRUJZ-T (Note 3)    | V3              | 2.8                           | -40°C to +85°C  | 6 Ld μTDFN           | L6.1.6X1.6     |

| ISL9021AIRUFZ-T (Note 3)    | V2              | 2.5                           | -40°C to +85°C  | 6 Ld μTDFN           | L6.1.6X1.6     |

| ISL9021AIRUCZ-T (Note 3)    | S6              | 1.8                           | -40°C to +85°C  | 6 Ld μTDFN           | L6.1.6X1.6     |

| ISL9021AIRUBZ-T (Note 3)    | VO              | 1.5                           | -40°C to +85°C  | 6 Ld μTDFN           | L6.1.6X1.6     |

| ISL9021AIRUWZ-T (Note 3)    | V7              | 1.2                           | -40°C to +85°C  | 6 Ld μTDFN           | L6.1.6X1.6     |

#### NOTES:

- 1. Please refer to TB347 for details on reel specifications.

- These Intersil Pb-free WLCSP and BGA packaged products employ special Pb-free material sets; molding compounds/die attach materials and SnAgCu - e1 solder ball terminals, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free WLCSP and BGA packaged products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 3. These Intersil Pb-free plastic packaged products employ special Pb-free material sets; molding compounds/die attach materials and NiPdAu plate-e4 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 4. For Moisture Sensitivity Level (MSL), please see device information page for ISL9021A. For more information on MSL please see techbrief TB363.

### **Absolute Maximum Ratings**

| Supply Voltage (VIN) | +6.5V        |

|----------------------|--------------|

| All Other Pins0.3 to | (VIN + 0.3)V |

### **Recommended Operating Conditions**

| Ambient Temperature Range (T <sub>A</sub> )40 | °C to +85°C   |

|-----------------------------------------------|---------------|

| Supply Voltage (V <sub>IN</sub> )             | . 1.5 to 5.5V |

| ESD Rating                                    |               |

| Human Body Model                              | 5000V         |

| Machine Model                                 | 250V          |

| Charged Device Model                          | 2200V         |

| Latch-Up Passed at +85°C                      | 100mA         |

#### **Thermal Information**

| Thermal Resistance (Typical)             | $\theta_{JA}(^{\circ}C/W)$ | θ <sub>JC</sub> (°C/W) |

|------------------------------------------|----------------------------|------------------------|

| 4 Ball WLCSP (Note 5)                    | 135.64                     | N/A                    |

| 6 Lead μTDFN (Notes 6, 7)                | 230                        | 93                     |

| Junction Temperature Range               | 40                         | 0°C to +125°C          |

| Operating Temperature Range              |                            | 40°C to +85°C          |

| Storage Temperature Range                | 6!                         | 5°C to +150°C          |

| Pb-Free Reflow Profile                   |                            | see link below         |

| http://www.intersil.com/pbfree/Pb-FreeRe | eflow.asp                  |                        |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 5. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 6. θ<sub>JA</sub> is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

- 7. For  $\theta_{\mbox{\scriptsize JC}},$  the "case temp" location is taken at the package top center.

**Electrical Specifications**  $T_A = -40 \,^{\circ}\text{C}$  to  $+85 \,^{\circ}\text{C}$ ;  $V_{\text{IN}} = (V_{\text{O}} + 0.5\text{V})$  to 5.5V with a minimum  $V_{\text{IN}}$  of 1.5V;  $C_{\text{IN}} = 1 \mu\text{F}$ ;  $C_{\text{O}} = 1 \mu\text{F}$ . Boldface limits apply over the operating temperature range, -40°C to +85°C.

| PARAMETER                            | SYMBOL             | TEST CONDITIONS                                                                                   | MIN<br>(Note 10) | TYP        | MAX<br>(Note 10) | UNIT                  |

|--------------------------------------|--------------------|---------------------------------------------------------------------------------------------------|------------------|------------|------------------|-----------------------|

| DC CHARACTERISTICS                   | 1                  |                                                                                                   |                  |            | '                |                       |

| Supply Voltage                       | V <sub>IN</sub>    |                                                                                                   | 1.5              |            | 5.5              | V                     |

| V <sub>IN</sub> Undervoltage Lockout | V <sub>UVLO+</sub> | V <sub>IN</sub> Rising                                                                            |                  | 1.425      | 1.5              | V                     |

| Threshold                            | V <sub>UVLO-</sub> | V <sub>IN</sub> Falling                                                                           | 1.3              | 1.375      |                  | V                     |

| Ground Current                       | I <sub>DD</sub>    | Output Enabled; I <sub>O</sub> = 0; V <sub>IN</sub> = 1.5V to 5.5V                                |                  | 35         | 50               | μΑ                    |

| Shutdown Current                     | I <sub>DDS</sub>   | V <sub>IN</sub> = 5.5V, EN = Low, I <sub>O</sub> = 0                                              |                  | 0.1        | 1.0              | μΑ                    |

| Output Voltage Accuracy              |                    | $V_{IN} = V_0 + 0.5V$ to 5.5V, $I_0 = 1$ mA to 250mA, $T_J = +25$ °C                              | -0.8             |            | +0.8             | %                     |

|                                      |                    | $V_{IN} = V_{O} + 0.5V$ to 5.5V, $I_{O} = 1$ mA to 250mA, $T_{J} = -40$ °C to +125 °C             | -1.8             |            | +1.8             | %                     |

| Maximum Output Current               | I <sub>MAX</sub>   | Continuous                                                                                        | 250              |            |                  | mA                    |

| Internal Current Limit               | I <sub>LIM</sub>   |                                                                                                   | 260              |            |                  | mA                    |

| Dropout Voltage (Notes 8, 9)         | V <sub>DO</sub>    | I <sub>0</sub> = 250mA; V <sub>0</sub> > 1.8V                                                     |                  | 150        | 250              | mV                    |

| Thermal Shutdown Temperature         | T <sub>SD</sub>    |                                                                                                   |                  | 160        |                  | °C                    |

| Thermal Shutdown Hysteresis          |                    |                                                                                                   |                  | 20         |                  | °C                    |

| AC CHARACTERISTICS                   | 1                  |                                                                                                   | l                | I          |                  |                       |

| Ripple Rejection (Note 8)            |                    | V <sub>IN</sub> = 4.5V, V <sub>0</sub> = 3.3V @ 1kHz                                              |                  | 60         |                  | dB                    |

|                                      |                    | V <sub>IN</sub> = 4.5V, V <sub>O</sub> = 3.3V @ 10kHz                                             |                  | 75         |                  | dB                    |

|                                      |                    | V <sub>IN</sub> = 4.5V, V <sub>0</sub> = 3.3V @ 1MHz                                              |                  | 50         |                  | dB                    |

| Output Noise Voltage (Note 8)        |                    | $V_{IN} = 4.2V$ , $T_A = +25$ °C, BW = 10Hz to 100kHz, $I_0 = 10$ mA                              |                  | 8.5*V<br>0 |                  | μV <sub>RM</sub><br>S |

| DEVICE START-UP CHARACTER            | ISTICS             |                                                                                                   |                  |            |                  |                       |

| Device Enable Time                   | t <sub>EN</sub>    | Time from assertion of the EN pin to when the output voltage reaches 95% of the $\rm V_{0}$ (nom) |                  | 250        | 600              | μs                    |

| LD0 Soft-start Ramp Rate             | t <sub>SSR</sub>   | Slope of linear portion of LDO output voltage ramp during start-up                                |                  | 30         | 60               | μs/V                  |

intersil FN7845.0 May 27, 2011

**Electrical Specifications**  $T_A = -40 \,^{\circ}\text{C}$  to  $+85 \,^{\circ}\text{C}$ ;  $V_{\text{IN}} = (V_{\text{O}} + 0.5\text{V})$  to 5.5V with a minimum  $V_{\text{IN}}$  of 1.5V;  $C_{\text{IN}} = 1 \mu\text{F}$ ;  $C_{\text{O}} = 1 \mu\text{F}$ . Boldface limits apply over the operating temperature range, -40  $\,^{\circ}\text{C}$  to +85  $\,^{\circ}\text{C}$ . (Continued)

| PARAMETER                | SYMBOL                           | TEST CONDITIONS | MIN<br>(Note 10) | TYP | MAX<br>(Note 10) | UNIT |

|--------------------------|----------------------------------|-----------------|------------------|-----|------------------|------|

| EN LOGIC CHARACTERISTICS |                                  |                 |                  |     |                  |      |

| Input Low Voltage        | V <sub>IL</sub>                  |                 |                  |     | 0.4              | V    |

| Input High Voltage       | V <sub>IH</sub>                  |                 | 1.1              |     |                  | V    |

| Input Leakage Current    | I <sub>IL,</sub> I <sub>IH</sub> |                 |                  |     | 0.1              | μΑ   |

#### NOTES:

- 8. Limits established by characterization and are not production tested.

- 9. Dropout voltage is measured as  $V_{IN}$   $V_{O}$ , when  $V_{O}$  is 4% lower than the value of  $V_{O}$

- 10. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

### **Typical Operating Performance**

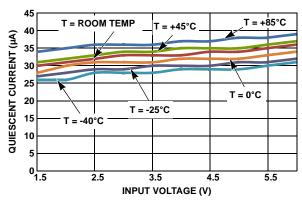

FIGURE 2. QUIESCENT CURRENT vs INPUT VOLTAGE (V<sub>OUT</sub> = 0.9V)

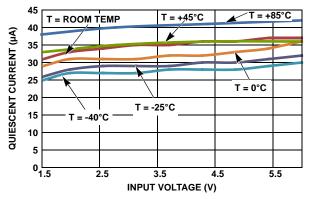

FIGURE 3. QUIESCENT CURRENT vs INPUT VOLTAGE  $(V_{OUT} = 1.85V)$

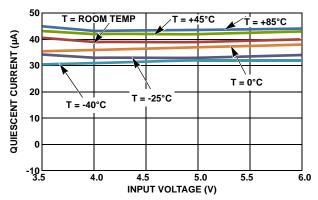

FIGURE 4. QUIESCENT CURRENT vs INPUT VOLTAGE (V<sub>OUT</sub> = 3.3V)

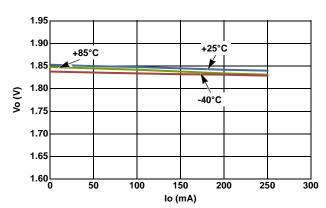

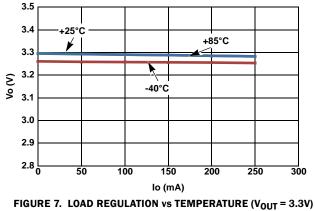

FIGURE 5. LOAD REGULATION vs TEMPERATURE (V<sub>OUT</sub> = 1.85V)

### **Typical Operating Performance** (Continued)

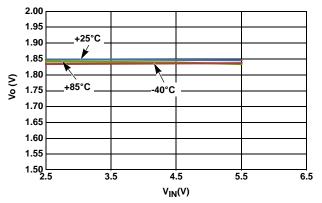

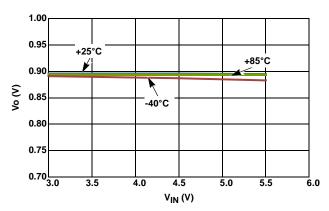

FIGURE 6. LINE REGULATION vs TEMPERATURE (V<sub>OUT</sub> = 1.85V)

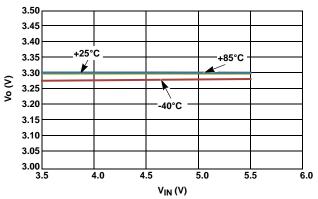

FIGURE 8. LINE REGULATION vs TEMPERATURE ( $V_{OUT} = 3.3V$ )

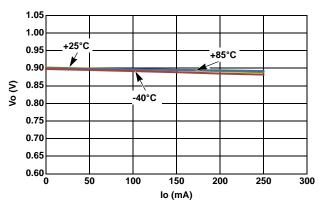

FIGURE 9. LOAD REGULATION vs TEMPERATURE ( $V_{OUT} = 0.9V$ )

FIGURE 10. LINE REGULATION vs TEMPERATURE ( $V_{OUT} = 0.9V$ )

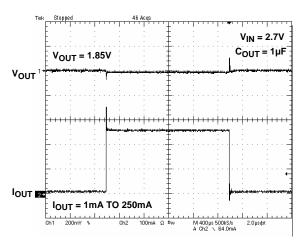

FIGURE 11. LOAD TRANSIENT RESPONSE

### **Typical Operating Performance (Continued)**

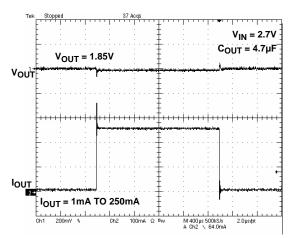

FIGURE 12. LOAD TRANSIENT RESPONSE

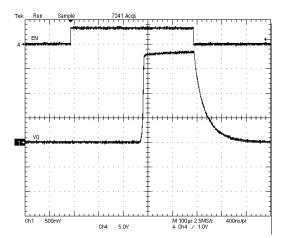

FIGURE 13. ENABLE FUNCTION (VIN = 3.6V, VOUT = 1.85V, COUT 1 $\mu$ F)

FIGURE 14. POWER SUPPLY REJECTION vs FREQUENCY

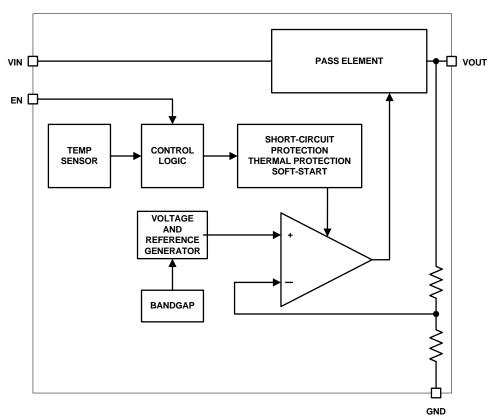

### **Functional Description**

The ISL9021A is a high performance low-dropout regulator (LDO) with 250mA sourcing capability. The extra low ground current makes this part a good choice for handheld product applications. The device also incorporates overcurrent, thermal shutdown, reverse current protections, and soft-start features.

Thermal shutdown protects the device against overheating. Soft-start limits the start-up input current surges. In some applications, the output voltage may be externally pulled higher than the input, or the input voltage could be connected to ground, or connected to some voltage lower than the output side. The ISL9021A features reverse current protection; that can block the reverse current from output to input.

#### **Enable Control**

The ISL9021A has an enable pin. When EN is low, the IC is in shutdown mode. In this condition, all on-chip circuits are off, and the device draws minimum current, typically less than  $0.1\mu A(typ)$ . Driving this pin high will turn on the device.

#### **LDO Protections**

The ISL9021A offers several protection functions, making it ideal for use in battery-powered applications. The ISL9021A provides short-circuit protection by limiting the output current at current limit of 260mA (min). If the short circuit lasts long enough, the die temperature increases, and the over-temperature protection circuit will shut down the output. When the die temperature reaches about +145°C, thermal protection starts to work with output being loaded with at least 50mA. Once the die temperature drops to about +110°C, the LDO will resume operation beginning with a soft-start.

The ISL9021A's reverse current protection is intended to block reverse conduction if output voltage is higher than input voltage.

### **Input and Output Capacitors**

The ISL9021A provides a linear regulator that has low quiescent current, fast transient response, and overall stable operation across the recommended operating conditions. A ceramic capacitor (X5R or X7R) with a capacitance of  $1\mu F$  to  $4.7\mu F$  with an ESR up to  $400m\Omega$  is suitable for the ISL9021A to maintain its output stability. The ground connection of the output capacitor should be routed directly to the GND pin of the device, and also placed close to the IC. Similarly for the input capacitor, usually a  $1\mu F$  ceramic capacitor (X5R or 7R) is suitable for most cases, but if a large, fast rising load transient condition is expected, a higher value input capacitor may be necessary to achieve satisfactory performance.

#### **Board Layout Recommendations**

A good PCB layout is an important step to achieve good performance. It is recommended to design the board with separate ground planes for input and output, and connect both ground planes at the GND pin of the IC. Consideration should be taken when placing the components and routing the trace to minimize the ground impedance, and keep the parasitic inductance low. Usually the input/output capacitors should be placed as close to the IC as possible with a good ground connection

### **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to web to make sure you have the latest revision.

| DATE         | REVISION | CHANGE          |

|--------------|----------|-----------------|

| May 27, 2011 | FN7845.0 | Initial Release |

### **Products**

Intersil Corporation is a leader in the design and manufacture of high-performance analog semiconductors. The Company's products address some of the industry's fastest growing markets, such as, flat panel displays, cell phones, handheld products, and notebooks. Intersil's product families address power management and analog signal processing functions. Go to <a href="https://www.intersil.com/products">www.intersil.com/products</a> for a complete list of Intersil product families.

\*For a complete listing of Applications, Related Documentation and Related Parts, please see the respective device information page on intersil.com: ISL9021A

To report errors or suggestions for this datasheet, please go to: <a href="www.intersil.com/askourstaff">www.intersil.com/askourstaff</a>

FITs are available from our website at: http://rel.intersil.com/reports/search.php

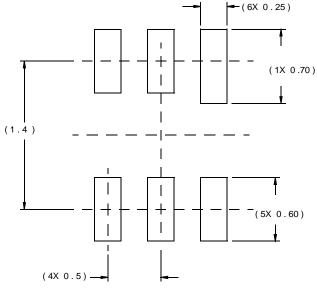

### **Package Outline Drawing**

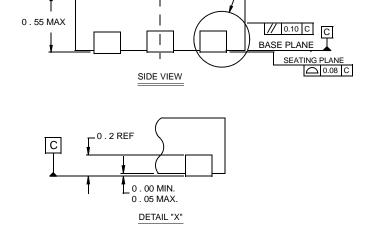

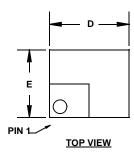

### L6.1.6x1.6

### 6 LEAD ULTRA THIN DUAL FLAT NO-LEAD COL PLASTIC PACKAGE (UTDFN COL)

Rev 1, 11/07

TYPICAL RECOMMENDED LAND PATTERN

#### NOTES:

- Dimensions are in millimeters.

Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to AMSE Y14.5m-1994.

- 3. Unless otherwise specified, tolerance : Decimal  $\pm 0.05$

- 4. Dimension b applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- 5. Tiebar shown (if present) is a non-functional feature.

- The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.

SEE DETAIL "X"

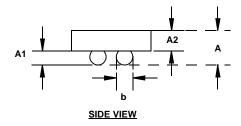

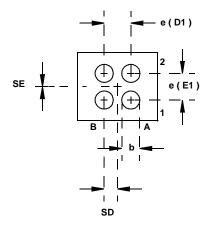

W2x2.4

## Wafer Level Chip Scale Package (WLCSP 0.4mm Ball Pitch)

| SYMBOL             | MILLIMETERS                   |  |  |

|--------------------|-------------------------------|--|--|

| А                  | 0.44 Min, 0.495 Nom, 0.55 Max |  |  |

| A1                 | 0.190 ±0.030                  |  |  |

| A2                 | 0.305 ±0.025                  |  |  |

| b                  | 0.270 ±0.030                  |  |  |

| D                  | 1.155 ±0.020                  |  |  |

| D1                 | 0.400 BASIC                   |  |  |

| E                  | 0.975 ±0.020                  |  |  |

| E1                 | 0.400 BASIC                   |  |  |

| е                  | 0.400 BASIC                   |  |  |

| SD                 | 0.200 BASIC                   |  |  |

| SE                 | 0.00 BASIC                    |  |  |

| NUMBER OF BUMPS: 4 |                               |  |  |

2x2 ARRAY 4 BALL WAFER LEVEL CHIP SCALE PACKAGE

Rev. 2 6/08

#### NOTES:

1. All dimensions are in millimeters.

**BOTTOM VIEW**

For additional products, see <a href="https://www.intersil.com/product-tree">www.intersil.com/product-tree</a>

Intersil products are manufactured, assembled and tested utilizing ISO9000 quality systems as noted in the quality certifications found at <a href="https://www.intersil.com/design/quality">www.intersil.com/design/quality</a>

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see <a href="https://www.intersil.com">www.intersil.com</a>